ROM y RAM en el BRAZO

Estoy trabajando en un procesador ARM, me pregunté si la ROM y la RAM utilizadas son bastante diferentes de lo que asumo. Por ejemplo, para un programa que tenga la siguiente tabla de memoria:

Program Size:

Code=1264

RO-data=16

RW-data=0

ZI-data=1384

¿Cómo se distribuye esto entre ROM y RAM?

4 answers

Dices " diferente de lo que pensamos ", como si todos pensaran de la misma manera:)

Supongo que viene de microcontroladores de gama baja que a menudo tienen espacios de dirección de datos y programas separados. En ARM la situación es diferente: el código del programa, los datos y los registros periféricos residen todos en el mismo espacio de memoria plano de 32 bits. Se dice que utilizan una arquitectura llamada "Harvard modificada": los buses de datos e instrucciones están separados * (Harvard), pero usan un solo espacio de memoria (Von Neumann). Por lo tanto, puede leer datos de ROM y ejecutar programas desde RAM sin ninguna configuración especial.

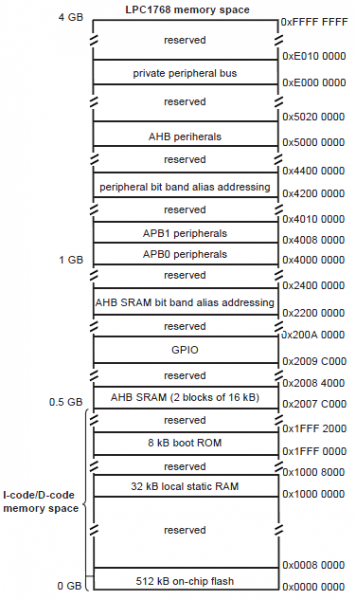

Por ejemplo, aquí está el mapa de memoria de LPC1768, un microcontrolador Cortex-M3 común de NXP.

Tenga en cuenta que en brazos más grandes el mapa puede ser mucho más complejo, por ejemplo, generalmente hay varias regiones CS (chip select) para flash externo / SRAM / SDRAM u otros periféricos, que pueden o no estar conectados para cada dispositivo específico utilizando procesador. Sin embargo, todos siguen siendo accesibles a través del mismo espacio de memoria plana de 32 bits.

Ahora sobre la línea que cita. Supongo que fue producido por Keil o ARM RVCT compiler. Las abreviaturas significan lo siguiente: RO = solo lectura, RW = lectura-escritura, ZI = cero inicializado.

Cuando compila un firmware independiente para un microcontrolador (a diferencia de un programa en modo usuario que se ejecuta en un sistema operativo), al final generalmente obtiene una sola imagen monolítica que se flasheará en el flash ROM y ejecutado en el lugar. Esto está bien para el código que generalmente no es modificado, o datos de solo lectura (const), pero no es tan bueno para datos de escritura. Ahí es donde entran las regiones RW y ZI. El compilador inserta un pequeño código de arranque que toma un fragmento con los valores iniciales de los datos inicializados de la imagen ROM y lo copia en la RAM (esta es la región RW). Luego se pone a cero el resto de la RAM utilizada (región ZI). A continuación, el control se transfiere al código real escrito por el programador.

Aquí traté de ilustrar cómo se ve un programa típico para el LPC1768 mencionado anteriormente:

+-----------+ 0x1000 8000 \

| Unused | |

+-----------+ |

| ZI data | <--(clear) | RAM

+-----------+ |

| RW data | <--(copy)---|---+

+-----------+ 0x1000 0000 / |

|

|

+-----------+ 0x0008 0000 \ |

| Unused | | |

+-----------+ | |

| RW init |-------------|---+

+-----------+ |

| RO data | | ROM (Flash)

+-----------+ |

| User code | |

+-----------+ |

| Boot code | |

+-----------+ |

| Vectors | |

+-----------+ 0x0000 0000 /

Por lo tanto, para calcular el espacio ROM (flash) utilizado, debe agregar código, RO-data y RW-data. La RAM utilizada será la suma de RW-data y ZI-data. Así que, para su caso, es 1264+16+0 = 1280 bytes de flash y 0 + 1384 = 1384 bytes de RAM.

*: no siempre es cierto: Yo creo que Los chips Cortex-M0 tienen un solo bus de datos/instrucciones.

Warning: date(): Invalid date.timezone value 'Europe/Kyiv', we selected the timezone 'UTC' for now. in /var/www/agent_stack/data/www/ajaxhispano.com/template/agent.layouts/content.php on line 61

2011-03-25 16:08:14

Igor Skochinsky te dio una buena explicación (en mi mente). Te daré basado en lo que pude averiguar con las herramientas de construcción de KEIL para un LPC23xx.

Si tiene la posibilidad de generar el archivo de mapa después de la compilación (en keil IDE esta es una opción de casilla de verificación simple en la configuración de compilación) abra el archivo y al final verá las siguientes líneas:

Total RO Size (Code+Ro data) 36732 (35.87kB)

Total RW Size (RW Data + ZI Data) 27348 (26.71kB

Total ROM Size (Code + RO Data + RW Data) 36812 (35.95kB

Creo que eso se explica por sí mismo, los datos RO residen en ROM y RW en RAM.

Warning: date(): Invalid date.timezone value 'Europe/Kyiv', we selected the timezone 'UTC' for now. in /var/www/agent_stack/data/www/ajaxhispano.com/template/agent.layouts/content.php on line 61

2013-06-19 09:16:02

Cómo se distribuye entre ROM y RAM depende de usted, debe decirle al enlazador dónde poner las cosas. Lo ideal sería que el código, que es de solo lectura, esté en rom, no use la memoria ram para eso. Del mismo modo, los datos de solo lectura pueden ir en rom. read write y zero init necesitan ir en ram.

¿Qué cadena de herramientas (basada en gcc, IAR, Keil, ARM, etc.) está utilizando?

Warning: date(): Invalid date.timezone value 'Europe/Kyiv', we selected the timezone 'UTC' for now. in /var/www/agent_stack/data/www/ajaxhispano.com/template/agent.layouts/content.php on line 61

2011-03-25 18:16:33

Lo ideal sería que el código, que es de solo lectura, estuviera en rom

Además, desea que su almacenamiento de código sea no volátil!